클럭 신호

"오늘의AI위키"의 AI를 통해 더욱 풍부하고 폭넓은 지식 경험을 누리세요.

1. 개요

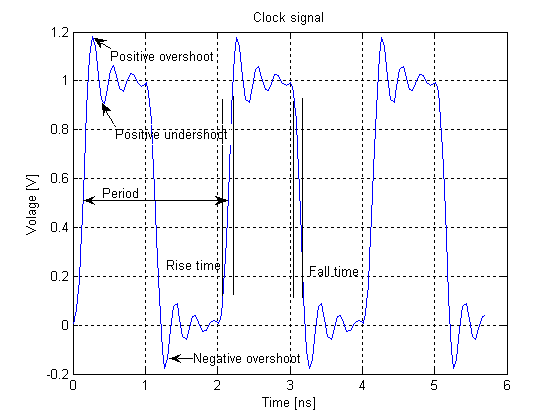

클럭 신호는 디지털 회로의 동기화를 위해 사용되는 주기적인 신호이다. 일반적으로 수정 발진기를 통해 생성되며, 피어스 발진 회로와 같은 회로를 통해 구현될 수 있다. 클럭 신호는 디지털 회로의 각 부분의 동작 시점을 정의하며, 마이크로프로세서와 같은 복잡한 시스템에서 특히 중요하다. 클럭 주파수는 회로의 속도를 나타내며, 클럭 승수를 통해 외부 클럭을 내부적으로 증가시킬 수 있다. 클럭 신호는 단상, 2상, 4상 클럭 등 다양한 형태로 사용되었으며, 현대에는 단상 클럭이 주로 사용된다. 클럭 신호는 클럭 분배 네트워크를 통해 칩 전체에 전달되며, 클럭 스큐를 최소화하는 것이 중요하다.

더 읽어볼만한 페이지

- 클럭 신호 - 클럭 속도

클럭 속도는 CPU의 주기적인 신호 속도로 헤르츠(Hz) 단위로 측정되며, CPU 성능에 영향을 미치지만 아키텍처 등 다른 요인과 함께 고려해야 하고, 오버클럭킹은 성능 향상과 함께 시스템 불안정의 위험이 있다. - 클럭 신호 - 클럭 게이팅

클럭 게이팅은 디지털 회로에서 불필요한 클럭 신호 전달을 막아 전력 소모를 줄이는 기술로, 저전력 장치에 필수적으로 활용되며, RTL 코딩 등을 통해 설계에 적용되어 에너지 효율성을 높이는 데 기여한다. - 디지털 회로 - 타이머

타이머는 시간 간격을 측정하거나 제어하는 장치 또는 기능으로, 기계식부터 전자식, 디지털, 소프트웨어 방식 등 다양한 형태로 존재하며, 독립적으로 사용되거나 시스템 내부에 내장되어 폭넓게 활용되고, 작동 방식과 구현 방식에 따라 여러 종류로 나뉘며, 최근에는 모바일 기반 타이머와 인공지능 기술을 활용한 효율적인 시간 관리 기능으로 발전하고 있다. - 디지털 회로 - 스위칭 회로 이론

- 회로 설계 - 허니웰

허니웰은 1885년 설립된 기업으로, 항공우주, 빌딩 자동화, 안전 및 생산성 솔루션, 성능 소재 및 기술 분야에서 사업을 영위하며, 군사 기술 개발 및 펜탁스 카메라 수입업체로 활동했고, 환경 문제 관련 비판을 받기도 한다. - 회로 설계 - 회로도

회로도는 전기 또는 전자 회로의 구성 요소와 연결을 기호와 선으로 나타낸 도식적 표현으로, 표준화된 기호와 규칙을 따르며 전자 제품 설계 및 교육에 필수적인 도구이지만 표기법 통일은 아직 완벽하지 않다.

| 클럭 신호 | |

|---|---|

| 개요 | |

| 유형 | 전기 신호 |

| 주요 용도 | 동기 회로에서 타이밍 및 동작을 제어 컴퓨터 및 디지털 회로에서 사용 마이크로프로세서 및 메모리와 같은 구성 요소 간의 데이터 전송을 동기화 |

| 특성 | |

| 주기 | 반복되는 시간 간격 |

| 주파수 | 초당 반복 횟수 (헤르츠 단위) |

| 듀티 사이클 | 한 주기 내에서 신호가 높은 상태인 시간 비율 |

| 상승 시간 | 낮은 상태에서 높은 상태로 변하는 데 걸리는 시간 |

| 하강 시간 | 높은 상태에서 낮은 상태로 변하는 데 걸리는 시간 |

| 지터 | 클럭 신호의 가장자리가 이상적인 위치에서 벗어나는 현상 |

| 생성 방법 | |

| 발진기 | 수정 발진기, LC 발진기, 링 발진기 등 다양한 발진기 회로를 사용하여 생성 |

| 클럭 제너레이터 | 특수 IC를 사용하여 생성 |

| 신호 생성기 | 테스트 및 측정용 신호 생성기를 사용하여 생성 |

| 관련 용어 | |

| 더블 데이터 레이트 (DDR) | 클럭 신호의 상승 및 하강 가장자리 모두에서 데이터를 전송하는 기술 |

| 클럭 도메인 | 동일한 클럭 신호에 의해 동기화된 회로의 영역 |

| 클럭 스큐 | 회로 내에서 클럭 신호가 서로 다른 시간에 도착하는 현상 |

| 추가 정보 | |

| 클럭 신호의 중요성 | 디지털 시스템에서 데이터 전송과 처리를 정확하게 제어하기 위해 필수적 |

| 클럭 신호 품질 | 지터, 스큐 등의 요인이 시스템 성능에 큰 영향을 미침 |

| 클럭 신호 배포 | 클럭 신호는 여러 구성 요소에 동시에 전달되어야 함 |

| 클럭 신호의 종류 | 싱글 엔드 클럭 차동 클럭 |

| 기타 | |

| 표준 | 전기 전자 부품 일반 용어 정보 처리 용어 |

2. 클럭 신호의 생성

집적 회로(IC)는 회로의 여러 부분을 동기화하기 위해 클럭 신호를 사용하며, 최악의 경우 내부 전파 지연 시간보다 느린 속도로 순환한다. IC가 더욱 복잡해짐에 따라 모든 회로에 정확하고 동기화된 클럭을 공급하는 문제는 점점 더 어려워진다. 이러한 복잡한 칩의 대표적인 예는 현대 컴퓨터의 중앙 구성 요소인 마이크로프로세서이며, 결정 발진기의 클럭에 의존한다. 비동기 회로와 같은 비동기 CPU는 예외이다.

규모와 복잡성을 가진 집적회로(IC)는 회로 각 부분의 지연 전파에서 최악의 경우를 고려하여, 그보다 낮은 주기로 각 부분을 동기화하기 위해 클럭 신호를 사용한다. 소정의 동작을 완료하는 데 여러 개의 클럭 주기(클럭 사이클)가 걸리는 경우도 있다. 대규모이고 복잡한 IC에서는 회로 전체에 정확하게 동기화된 클럭을 공급하는 것 자체도 어려워진다. 대표적인 예로 마이크로프로세서가 있으며, 수정 발진기를 이용한 발진 회로를 사용하여 발생시킨다. 저속 동작 기기나 정밀도를 요구하지 않는 기기에서는 세라믹 발진기를 사용하기도 한다. 수정 발진기와 발진 회로를 하나의 패키지에 내장하여 전원을 연결하기만 하면 클럭 신호를 출력하는 '''클럭 모듈'''이라는 전자 부품을 사용하기도 한다.

클럭 신호는 게이트 제어될 수도 있다. 즉, 회로의 특정 부분에 대한 클럭 신호 공급 여부를 다른 신호로 제어한다. 사용되지 않는 디지털 회로의 일부를 정지시켜 소비 전력을 줄이는 데 이 기법을 사용하지만, 타이밍 분석의 복잡성이 증가한다.

2. 1. 수정 발진기

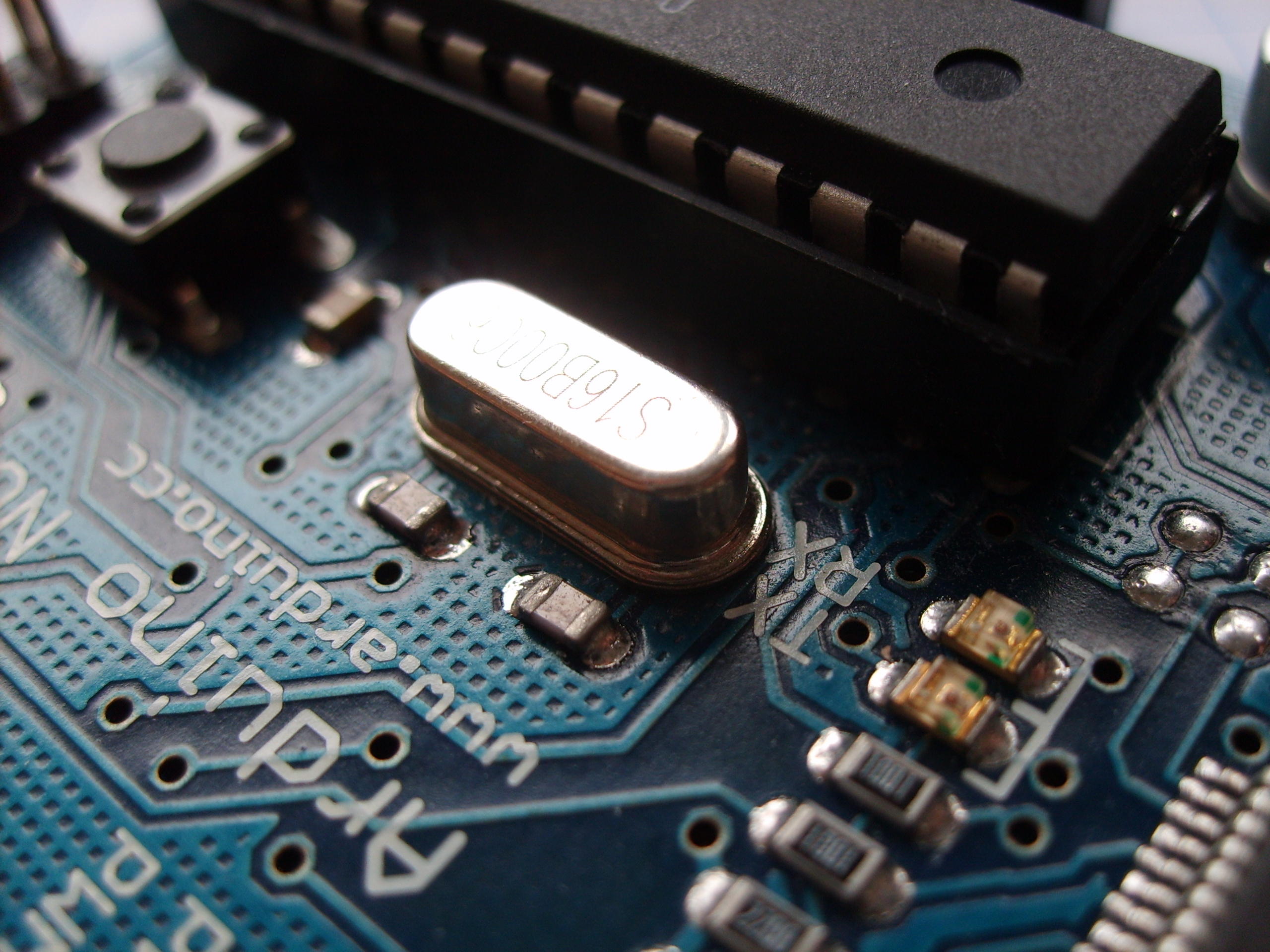

디지털 회로에서 사용하는 클럭은 대부분 수정 발진기(quartz crystal oscillator, 수정 발진자라고도 함)를 통해 만들어진다. 수정 발진자는 수정을 가공하여 만든 얇은 조각(박편) 양극에 특정 주파수를 입력하면, 자신의 고유 주파수만 걸러내어 고유한 주파수를 발생시키는 소자이다. 입력된 주파수를 자기 공진 주파수가 되도록 유도하는 방식으로 클럭이 발생한다. 수정 발진자는 가공 방식과 크기에 따라 주파수가 달라지지만, 너무 낮거나 높은 주파수는 발생에 한계가 있다.

수정 발진기 자체에 직류 전압을 인가하면 클럭 신호가 발생하지 않는다. 따라서 수정 발진기의 주파수 근처의 방형파를 만드는 전자 회로를 사용하여 수정 발진기에 신호를 인가하면, 수정 발진기는 자기 고유의 주파수만 공진시켜 전자 회로가 해당 주파수로 공진하도록 유도한다. 결국 전자 회로와 결합하여 발진 회로가 완성된다.

클럭 신호를 발진하면 이상적인 방형파는 불가능하다. 상승 또는 하강 엣지에서 상태 변화 시간이 필요하다.

| 전원 인가형 자체 발진 | 발진 회로와 결합한 수정 발진자 |

|---|---|

|  |

수정 발진자와 발진 회로의 결합 방식에 따라, 클럭 신호 발생 부품은 두 가지 형태로 나뉜다. 하나는 발진 회로와 수정 발진자를 결합하여 하나의 부품으로 만든 것이고, 다른 하나는 발진 회로 없이 수정 발진 자체만 기능하는 부품이다.

NOT 게이트 같은 논리 회로와 R-C 조합으로 수정 발진자에 정해진 주파수 근처를 인가하면 수정 발진자의 특정 주파수로 공진하게 할 수 있다. 보통 수정 발진자 없이 능동 소자와 R-L-C 등을 사용한 발진 회로로 주파수를 만들 수 있으나, 각 소자의 오차 등으로 인해 정확한 주파수를 얻기 어렵다.

2. 1. 1. 마이크로프로세서에서의 클럭 신호 발진

클럭 신호 발생 부품 자체에 발진 회로와 수정 발진자를 결합하여 하나의 부품으로 만들 수 있다. 이에 비해 발진 회로 없이 수정 발진 자체만 기능하는 부품도 있어 선택적으로 사용할 수 있다.수정 발진자와 그 부가 회로를 넣어 하나의 부품을 제작하고 Vcc-GND 전원을 인가하면 클럭 신호가 나온다. 따라서 수정 발진자에 필요한 주파수 발생 회로를 PCB에 별도로 추가할 필요가 없다. 그러나 수정 발진 기능만 하는 부품은 수정 발진자에 클럭을 인가하기 위한 회로와 부가 회로가 필요하다. 현실적으로 클럭을 발생하는 회로는 그리 어렵지 않다. 단지 콘덴서를 반도체 부품에 넣는 것이 부담스럽기 때문에 20p 정도의 콘덴서 2개와 필요에 따라 저항 하나 정도면 반도체 내의 발진 회로와 PCB의 발진 회로가 결합하여 발진 회로 전체를 구성할 수 있다. 그래서 마이크로컨트롤러 등에는 수정 발진 기능만 있는 부품을 많이 사용한다.

내쇼널 세미컨덕터(National Semiconductor)의 IMP-16 계열과 같은 초기 마이크로프로세서는 다상 클럭을 사용했다. IMP-16의 경우 클럭은 4상이며, 각 위상은 90도씩 시간 차이가 있어 프로세서 코어와 주변 장치의 동기화에 사용되었다.

1970년대 MOS IC는 2상 클럭을 사용했다. 예를 들어 모토로라 MC6800과 8080은 외부에서 2상 클럭을 공급받았다. 모토로라의 전자 부품 제조 부문은 수정 발진기가 포함된 하이브리드 IC를 판매했다. 이러한 IC는 6800과 8080이 필요로 하는 겹치지 않는 2상 파형을 생성했다. 이후 인텔은 8224 클럭 제너레이터를, 모토로라는 MC6875를 생산했다. 인텔 8085와 모토로라 6802와 같은 차세대 마이크로프로세서는 클럭 제너레이터를 칩에 내장하게 되었다. 8080의 클럭 주파수는 2MHz였지만, 그 처리 성능은 1MHz의 6800과 거의 동등했다. 즉, 8080에서는 1명령의 처리에 더 많은 클럭 사이클이 걸린다. 6800은 최소 100kHz에서도 동작했지만, 8080은 클럭이 정지할 속도까지 동작 가능했다. 이러한 마이크로프로세서의 고속 버전은 1976년에 출시되었다.

6501은 외부 2상 클럭 제너레이터를 필요로 했다. 그 후속인 MOS 6502도 2상 클럭으로 구동하는 내부 설계였지만, 2상 클럭 제너레이터를 칩에 통합했기 때문에 외부에서는 단상 클럭만 입력하면 되어 시스템 설계가 간소화되었다. IC에 따라 4상 클럭을 필요로 하는 것도 있지만, 최근의 마이크로프로세서와 마이크로컨트롤러는 단상 클럭을 사용하고 있다.

2. 1. 2. 피어스 발진 회로

콜피츠 발진기에서 파생된 피어스 발진 회로(Pierce oscillator)는 디지털 회로에 사용하는 NOT 게이트와 수정 발진자, 저항(R), 그리고 커패시터(C)를 활용하여 쉽게 만들 수 있다.[21][22]

2. 1. 3. 수정 발진자의 활용

디지털 회로에서 사용하는 클럭은 대부분 수정 발진기(quartz crystal oscillator, 수정 발진자라고도 함)를 통해 만들어진다. 수정 발진자는 수정을 가공하여 만든 얇은 조각(박편) 양극에 특정 주파수를 입력하면, 자신의 고유 주파수만 걸러내어 고유한 주파수를 발생시키는 소자이다. 입력된 주파수를 자기 공진 주파수가 되도록 유도하는 방식으로 클럭이 발생한다. 수정 발진자는 가공 방식과 크기에 따라 주파수가 달라지지만, 너무 낮거나 높은 주파수는 발생에 한계가 있다.

수정 발진기 자체에 직류 전압을 인가하면 클럭 신호가 발생하지 않는다. 따라서 수정 발진기의 주파수 근처의 방형파를 만드는 전자 회로를 사용하여 수정 발진기에 신호를 인가하면, 수정 발진기는 자기 고유의 주파수만 공진시켜 전자 회로가 해당 주파수로 공진하도록 유도한다. 결국 전자 회로와 결합하여 발진 회로가 완성된다.

클럭 신호를 발진하면 이상적인 방형파는 불가능하다. 상승 또는 하강 엣지에서 상태 변화 시간이 필요하다.

| 전원 인가형 자체 발진 | 발진 회로와 결합한 수정 발진자 |

|---|---|

클럭 신호 발생 부품은 자체에 발진 회로와 수정 발진자를 결합하여 하나의 부품으로 만들거나, 발진 회로 없이 수정 발진 자체만 기능하는 부품으로 만들 수 있다. 전원 인가형 자체 발진 수정 발진자는 Vcc-GND 전원을 인가하면 클럭 신호가 나오므로, PCB 내에 별도의 주파수 발생 회로를 추가할 필요가 없다. 그러나 수정 발진 기능만 하는 부품은 클럭을 인가하기 위한 회로와 부가 회로가 필요하다.

현실적으로 클럭 발생 회로는 20pF 정도의 콘덴서 2개와 필요에 따라 저항 하나 정도면 반도체 내의 발진 회로와 PCB의 발진 회로가 결합하여 구성할 수 있을 정도로 간단하다. 그래서 마이크로컨트롤러 등에는 수정 발진 기능만 있는 부품을 많이 사용한다.

피어스[21][22] 발진 회로(Pierce oscillator)는 NOT 게이트와 수정 발진자, R, C를 활용하여 쉽게 만들 수 있는 콜피츠 발진기의 파생 회로이다.

NOT 게이트 같은 논리 회로와 R-C 조합으로 수정 발진자에 정해진 주파수 근처를 인가하면 수정 발진자의 특정 주파수로 공진하게 할 수 있다. 보통 수정 발진자 없이 능동 소자와 R-L-C 등을 사용한 발진 회로로 주파수를 만들 수 있으나, 각 소자의 오차 등으로 인해 정확한 주파수를 얻기 어렵다.

2. 2. 위상 동기 회로(PLL)를 이용한 클럭 신호 발진

위상동기회로(PLL) 방식의 회로를 구성하여 낮은 주파수의 수정발진기에서 높은 주파수를 얻을 수 있다.위상동기회로는 통신 등 여러 응용분야에서 사용되지만, 임베디드 CPU의 고속 클럭 발생회로에서도 사용된다.

임베디드 CPU는 높은 동작 주파수를 위해 PLL을 사용하는 경우가 많다.[23] 위상동기회로를 사용하면 디지털 회로 구성 요소의 카운터값을 변경하여 다른 주파수를 생성할 수 있다는 장점이 있다. 수정발진기 주파수 입력 '''FI'''가 고정된 상태에서 PLL의 되먹임 카운터 '''N'''을 프로그래밍 방식으로 조절하면 출력 주파수 '''FO'''로 다른 주파수를 얻을 수 있다.

이더넷 카드에 들어가는 디지털 회로는 25MHz에서 DPLL을 사용하여 원하는 주파수의 클럭을 생성한다.[24] 상대방이 보낸 데이터 신호에서 데이터를 추출하려면 데이터 비트의 시작과 끝 시간을 알아야 하는데, 25MHz 클럭 신호에서 DPLL을 사용하여 동기 클럭 신호를 얻는다.

3. 디지털 회로에서의 클럭 신호

대부분의 복잡한 집적 회로(IC)는 회로의 여러 부분을 동기화하기 위해 클럭 신호를 사용하며, 내부 전파 지연 시간보다 느린 속도로 순환한다. IC가 더욱 복잡해짐에 따라 모든 회로에 정확하고 동기화된 클럭을 공급하는 문제는 점점 더 어려워진다. 이러한 복잡한 칩의 대표적인 예는 현대 컴퓨터의 중앙 구성 요소인 마이크로프로세서이며, 결정 발진기의 클럭에 의존한다. 비동기 회로와 같은 비동기 CPU는 예외이다.

클럭 신호는 게이트될 수도 있다. 즉, 회로의 특정 부분에 대한 클럭 신호를 활성화하거나 비활성화하는 제어 신호와 결합될 수 있다. 이 기술은 사용하지 않는 디지털 회로 부분을 효과적으로 끄는 방식으로 전력을 절약하는 데 자주 사용되지만, 타이밍 분석의 복잡성이 증가한다.

3. 1. 클럭 신호의 종류

대부분의 현대적인 동기식 회로는 단상 클럭(single-phase clock)만을 사용하며, 이는 모든 클럭 신호가 하나의 와이어로 전송됨을 의미한다.[1][2][3][4]동기 회로에서 "2상 클럭"은 두 개의 와이어에 분배되는 클럭 신호를 말하며, 각 와이어는 겹치지 않는 펄스를 갖는다. 전통적으로 한 와이어는 "phase 1" 또는 "φ1"(파이)로, 다른 와이어는 "phase 2" 또는 "φ2" 신호를 전달한다. 두 상이 겹치지 않도록 보장되므로, 게이트형 래치를 엣지 트리거드 플립플롭 대신 사용하여 상태 정보를 저장할 수 있다.

1970년대 금속 산화물 반도체(MOS) IC는 일반적으로 이중 클럭 신호(2상 클럭)를 사용했다. 모토로라 6800 및 인텔 8080 마이크로프로세서가 그 예시이다.[5] 그러나 차세대 마이크로프로세서는 칩 상에 클럭 생성 기능을 통합했다.

6501은 외부 2상 클럭 발생기가 필요했지만, MOS 테크놀로지 6502는 2상 클럭 발생기를 칩에 내장하여 단일 상 클럭 입력만 필요로 했다.

초기 집적 회로는 4상 논리를 사용하는 경우가 있었는데, 이는 4개의 분리되고 겹치지 않는 클럭 신호로 구성된 4상 클럭 입력을 필요로 한다.[7] 내셔널 세미컨덕터 IMP-16, 텍사스 인스트루먼츠(Texas Instruments) TMS9900 등이 대표적인 예시이다.

하지만 대부분의 최신 마이크로프로세서와 마이크로컨트롤러는 단상 클럭을 사용한다.

3. 2. 클럭 주파수와 배율

많은 현대의 마이크로컴퓨터는 더 낮은 주파수의 외부 클럭을 마이크로프로세서의 적절한 클럭 속도로 곱하는 "클럭 승수"를 사용한다. 이를 통해 CPU는 컴퓨터의 다른 부분보다 훨씬 높은 주파수로 작동할 수 있으며, CPU가 외부 요소(메모리나 입출력 등)를 기다릴 필요가 없는 상황에서 성능 향상을 제공한다.1초 동안 진동하는(전압의 최대값과 최소값을 반복하는) 횟수를 '''클럭 주파수'''라고 한다. 컴퓨터에서 자주 "인텔 코어 i7 3.20GHz"와 같이 표시되는 것을 볼 수 있는데, 이 3.20GHz 부분이 클럭 주파수이다. 현대 컴퓨터에서 자주 사용하는 단위는 주로 기가헤르츠(GHz)이며, 이 값이 클수록 컴퓨터의 처리 속도가 빠르다는 것을 의미한다. 단, 1클럭당 처리 내용과 코어 수는 컴퓨터의 기종 및 제품에 따라 다르므로, 서로 다른 기종 및 제품 간에는 클럭 주파수만으로 성능을 비교할 수 없다.

최근 마이크로프로세서는 외부 클럭 주파수를 내부적으로 몇 배로 증가시켜 적절한 클럭 주파수로 동작한다. 따라서 컴퓨터 시스템 전체보다 CPU 부분만 고속으로 동작하며, CPU가 외부 요인(메모리 및 입출력)을 기다려야 할 때를 제외하고 성능 향상이 이루어진다. 시스템 전체에 공급되는 클럭을 '''베이스 클럭'''(Base Clock|베이스 클럭영어)[16], CPU의 배수를 '''CPU 멀티플라이어'''(CPU 레시오라고도 함)라고 한다.[17] 2022년 현재, x64 CPU의 베이스 클럭은 100MHz 전후로 설정되는 경우가 많다. 예를 들어 3.20GHz로 실제 동작 중인 CPU는 100MHz의 베이스 클럭에 x32 CPU 멀티플라이어를 적용하여 동작하고 있다.

3. 3. 동적 주파수 변경

대부분의 디지털 기기는 고정된 일정한 주파수의 클럭을 필요로 하지 않는다. 최소 및 최대 클럭 주기만 준수하면 클럭 에지 간의 시간은 이전 에지와 다음 에지 사이에서 크게 달라질 수 있다. 확산 스펙트럼 클럭 생성, 동적 주파수 스케일링 등과 같이 주파수를 동적으로 변경하는 클럭 발생기를 사용하는 디지털 기기는 동일하게 작동한다. 정적 논리를 사용하는 기기는 최대 클럭 주기(즉, 최소 클럭 주파수)가 없다. 이러한 기기는 무기한으로 속도를 늦추고 일시 정지한 후 언제든지 나중에 최대 클럭 속도로 다시 시작할 수 있다.4. 기타 회로에서의 클럭 신호

일부 민감한 혼성 신호 회로(예: 고정밀 아날로그-디지털 변환기)는 정방파 대신 정현파를 클럭 신호로 사용하는데, 이는 정방파에 포함된 고주파 고조파가 아날로그 회로에 간섭하여 잡음을 유발할 수 있기 때문이다. 이러한 사인파 클럭은 종종 차동 신호를 사용하는데, 이는 같은 전압 범위를 갖는 단일 종단 신호보다 두 배의 슬루율을 가지므로 타이밍 불확실성이 절반으로 줄어들기 때문이다. 차동 신호는 단일 라인보다 전자파 방출이 적다. 또는 전력선과 접지선으로 차폐된 단일 라인을 사용할 수도 있다.

CMOS 회로에서는 게이트 커패시턴스가 지속적으로 충전 및 방전된다.[1] 커패시터는 에너지를 소모하지 않지만, 구동 트랜지스터에서 에너지가 낭비된다.[1] 가역 연산에서는 인덕터를 사용하여 이 에너지를 저장하고 에너지 손실을 줄일 수 있지만, 인덕터는 크기가 상당히 큰 경향이 있다.[1]

또한, 컴퓨터 하드웨어나 운영 체제(OS)의 시계 기능(년월일시분초를 측정하는, 일반 시계와 동일한 기능)을 클럭이라고 부르는 경우도 있다. 그러한 하드웨어를 특히 RTC(속칭 CMOS 클럭)이라고 한다. 시판되는 개인용 컴퓨터의 RTC는 발진기 및 주변 회로의 정확도가 일반 시계만큼 높지 않고, 또한 OS에서는 개인용 컴퓨터의 범용 클럭을 사용하여 측정하기 때문에, 모두 일반 시계에 비해 오차가 발생하기 쉽다. 따라서 시간이 일치하는 것이 중요한 경우에는 NTP 등으로 정기적으로 보정할 필요가 있다.

5. 클럭 신호 분배

칩의 모든 부분에 클럭 신호를 스큐 없이 전달하는 가장 효과적인 방법은 금속 그리드 방식이다. 대형 마이크로프로세서에서 클럭 신호 구동에 사용되는 전력은 칩 전체 전력의 30%를 넘을 수 있다.[9][10] 게이트가 양 끝에 있고 그 사이에 모든 증폭기가 있는 전체 구조는 매 사이클마다 로드와 언로드를 반복해야 한다. 클럭 게이팅은 에너지를 절약하기 위해 트리의 일부를 일시적으로 차단하는 기술이다.

'''클럭 분배 네트워크'''(혹은 이 네트워크가 H-트리와 같은 트리 형태를 이룰 때 '''클럭 트리''')는 공통 지점에서 클럭 신호를 필요로 하는 모든 요소에 분배한다. 동기 시스템 작동에 매우 중요하기 때문에, 클럭 신호의 특성과 분배에 사용되는 전기 네트워크에 많은 관심이 주어져 왔다. 클럭 신호는 단순한 제어 신호로 간주되기도 하지만, 매우 특별한 특성과 속성을 가지고 있다.

클럭 신호는 일반적으로 가장 큰 팬아웃으로 로드되고 동기 시스템 내의 어떤 신호보다 가장 높은 속도로 작동한다. 데이터 신호는 클럭 신호에 의해 시간적 기준을 제공받기 때문에 클럭 파형은 특히 깨끗하고 선명해야 한다. 또한, 클럭 신호는 기술 축소(무어의 법칙 참조)의 영향을 특히 많이 받는데, 선의 크기가 감소함에 따라 긴 글로벌 상호연결선의 저항이 상당히 증가하기 때문이다. 이러한 선 저항의 증가는 동기 성능에 대한 클럭 분배의 중요성이 증가하는 주요 원인 중 하나이다. 클럭 신호의 도착 시간 차이와 불확실성을 제어하지 못하면 전체 시스템의 최대 성능을 심각하게 제한하고 잘못된 데이터 신호가 레지스터 내에 래치될 수 있는 치명적인 경합 조건을 만들 수 있다.

대부분의 동기 디지털 시스템은 각 레지스터 세트 사이에 조합 논리가 있는 순차 레지스터의 캐스케이드된 은행으로 구성된다. 디지털 시스템의 기능적 요구 사항은 논리 단계에 의해 충족된다. 각 논리 단계는 타이밍 성능에 영향을 미치는 지연을 도입하며, 디지털 설계의 타이밍 성능은 타이밍 분석을 통해 타이밍 요구 사항과 비교하여 평가할 수 있다. 타이밍 요구 사항을 충족하기 위해 특별한 고려 사항이 필요한 경우가 종종 있다. 예를 들어, 글로벌 성능 및 로컬 타이밍 요구 사항은 중요한 최악의 경우 타이밍 제약 조건을 충족하기 위해 균등하게 간격이 지정된 시간 창에 파이프라인 레지스터를 신중하게 삽입하여 충족될 수 있다. 클럭 분배 네트워크의 적절한 설계는 중요한 타이밍 요구 사항이 충족되고 경합 조건이 없도록 하는 데 도움이 된다(클럭 스큐 참조).

일반적인 동기 시스템을 구성하는 지연 구성 요소는 메모리 저장 요소, 논리 요소, 클럭킹 회로 및 분배 네트워크라는 세 가지 개별 하위 시스템으로 구성된다.

이러한 문제를 완화하고 효과적인 솔루션을 제공하기 위해 새로운 구조가 현재 개발 중이다. 중요한 연구 분야에는 공진 클럭킹 기술("공진 클럭 메시"),[11][12][13][14] 칩 상 광 상호 연결 및 로컬 동기화 방법론이 포함된다.

어느 정도 이상의 규모와 복잡성을 가진 집적회로(IC)는 회로 각 부분의 지연 전파에서 최악의 경우를 고려하여, 그보다 낮은 주기로 각 부분을 동기화하기 위해 클럭 신호를 사용하는 경우가 많다. 소정의 동작을 완료하는 데 여러 개의 클럭 주기(클럭 사이클)가 걸리는 경우도 있다. 더욱 대규모이고 복잡한 IC에서는 회로 전체에 정확하게 동기화된 클럭을 공급하는 것 자체도 어려워진다. 그 대표적인 예로 마이크로프로세서가 있으며, 일반적으로 수정 발진기를 이용한 발진 회로를 사용하여 발생시킨다. 저속 동작의 기기나 정밀도를 요구하지 않는 기기에서는 저렴한 세라믹 발진기를 사용하는 경우도 있다. 수정 발진기와 발진 회로를 하나의 패키지에 내장하여 전원을 연결하기만 하면 클럭 신호를 출력하는 '''클럭 모듈'''이라고 불리는 전자 부품을 사용하는 경우가 많다. 예외로 비동기 회로가 있다.

클럭 신호는 게이트 제어될 수도 있다. 즉, 회로의 특정 부분에 대한 클럭 신호 공급 여부를 다른 신호로 제어한다. 사용되지 않는 디지털 회로의 일부를 정지시켜 소비 전력을 저감시키는 데 이 기법을 사용하는 경우가 많지만, 타이밍 분석의 복잡성이 증가한다.

클록 신호가 왜곡되지 않고 칩의 각 부분에 도달하도록 하는 가장 효율적인 방법은 메탈 그리드이다. 대규모 마이크로프로세서에서는 클록 신호를 구동하고 분배하는 데 사용되는 전력이 칩 전체 소비 전력의 30% 이상을 차지하기도 한다. 클록 신호를 각 부분에 전달하는 회로를 클럭 분배 네트워크라고 한다. 여기에는 재귀적인 H 트리가 자주 사용된다. 그 네트워크 종단의 게이트를 포함한 전체 구조와 중간의 모든 증폭 회로는 매 사이클마다 로드와 언로드를 반복해야 한다. 클록 게이팅이라는 기술은 절전을 위해 사용하지 않는 부분의 클록 분배 네트워크를 일시적으로 차단한다.

참조

[1]

웹아카이브

Two-phase clock

https://web.archive.[...]

2007-11-09

[2]

웹사이트

Two-phase non-overlapping clock generator

https://web.archive.[...]

Tams-www.informatik.uni-hamburg.de

2012-01-08

[3]

웹사이트

Concepts in Digital Imaging - Two Phase CCD Clocking

http://micro.magnet.[...]

Micro.magnet.fsu.edu

2012-01-08

[4]

웹사이트

Cell cgf104: Two phase non-overlapping clock generator

https://web.archive.[...]

Hpc.msstate.edu

2012-01-08

[5]

저널

How to drive a microprocessor

http://commons.wikim[...]

McGraw-Hill

1976-04-15

[6]

저널

Intel's Higher Speed 8080 μP

https://web.archive.[...]

Microcomputer Associates

1975-09

[7]

웹사이트

Concepts in digital imaging - Four Phase CCD Clocking

http://micro.magnet.[...]

Micro.magnet.fsu.edu

2012-01-08

[8]

저널

A 20-MIPS sustained 32-bit CMOS microprocessor with high ratio of sustained to peak performance

1989

[9]

웹사이트

Intel's Atom Architecture: The Journey Begins

http://www.anandtech[...]

[10]

웹사이트

Alpha: The history in facts and comments

https://web.archive.[...]

2012-01-03

[11]

저널

Uniform-phase uniform-amplitude resonant-load global clock distributions

[12]

논문

Resonant clock mega-mesh for the IBM z13

https://ieeexplore.i[...]

[13]

논문

Modeling and optimization of low power resonant clock mesh

https://ieeexplore.i[...]

[14]

웹사이트

Clock tree synthesis

https://www.techdesi[...]

[15]

서적

bit 単語帳

共立出版

1990-08-15

[16]

웹사이트

動作周波数とは?

https://www.intel.co[...]

Intel

2022-04-08

[17]

웹사이트

動作周波数とは?

https://www.intel.co[...]

Intel

2022-04-08

[18]

웹인용

Spartan-3 FPGA Family Data Sheet

http://www.xilinx.co[...]

http://www.xilinx.com

2013-09-17

[19]

웹인용

Z80 Family CPU User Manual

http://www.zilog.com[...]

www.zilog.com

2013-09-17

[20]

웹인용

MC6809 8-Bit Microprocessing Unit

http://pdf.datasheet[...]

Motorola Microprocessor Data

2013-09-17

[21]

저널

Piezoelectric crystal resonators and crystal oscillators applied to the precision calibration of wavemeters

1923-10

[22]

특허

Electrical System

[23]

서적

S3C2440A 32-BIT RISC MICROPROCESSOR USER'S MANUAL

2004-06-30

[24]

웹인용

Phase Locked Loop

http://www.erg.abdn.[...]

http://www.erg.abdn.ac.uk

본 사이트는 AI가 위키백과와 뉴스 기사,정부 간행물,학술 논문등을 바탕으로 정보를 가공하여 제공하는 백과사전형 서비스입니다.

모든 문서는 AI에 의해 자동 생성되며, CC BY-SA 4.0 라이선스에 따라 이용할 수 있습니다.

하지만, 위키백과나 뉴스 기사 자체에 오류, 부정확한 정보, 또는 가짜 뉴스가 포함될 수 있으며, AI는 이러한 내용을 완벽하게 걸러내지 못할 수 있습니다.

따라서 제공되는 정보에 일부 오류나 편향이 있을 수 있으므로, 중요한 정보는 반드시 다른 출처를 통해 교차 검증하시기 바랍니다.

문의하기 : help@durumis.com